1588Tiny微型IP核

IEEE1588v2 無CPU從時鐘

1588 Tiny是用於Xilinx FPGA的IEEE1588-2008 V2從站僅硬兼容時鐘同步IP內核。它專注於需要使用最少資源的基本IEEE 1588功能的設備。1588 Tiny能夠準確地為IEEE 1588報文加上時間戳,並且僅使用硬件模塊也可提供同步時鐘。

不需要嵌入式處理器,也不需要通用的以太網MAC。1588 Tiny包括優化的以太網MAC,可以處理PTP幀。它支持電源配置文件和IEC 61850,還可以支持其他配置文件。

以下Xilinx FPGA系列支持1588 Tiny:

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

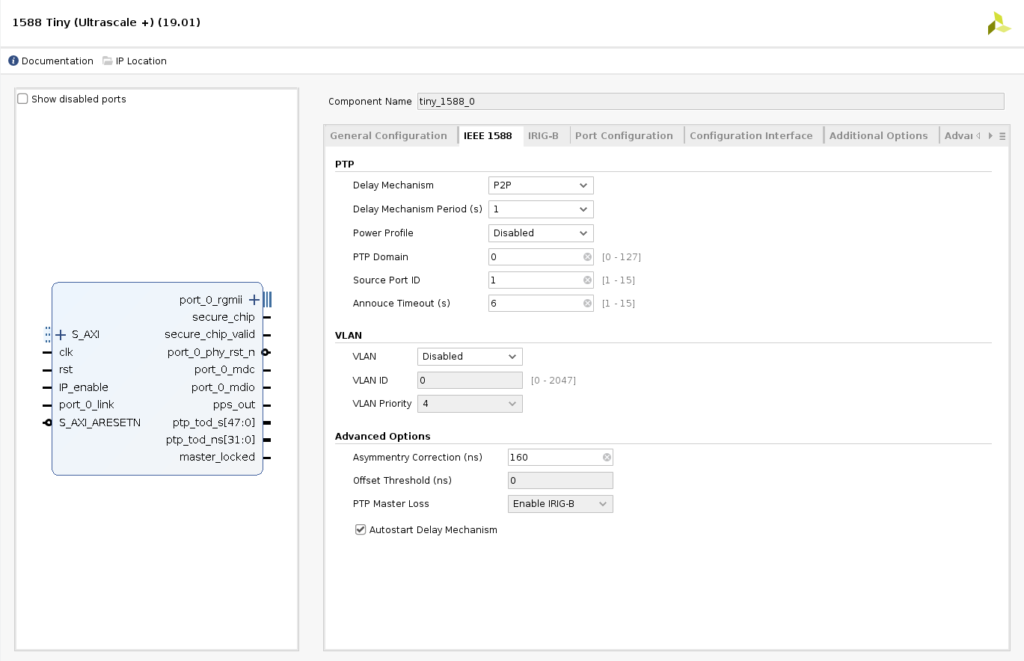

用於Xilinx Vivado工具的1588Tiny IP內核

通過利用新的Xilinx Vivado工具,可以輕松地將其集成到你的FPGA設計中,該工具允許在圖形用戶界面中使用IP內核,並以簡便的方式配置IP參數。

1588 Tiny 主要功能

一般

- 適用於Vivado(IP集成商)

- 支持單端口和雙端口(以太網接口可用於其他目的)模式

接口

- MII/RMII/GMII/RGMII/SGMII/QSGMII/USXGMII物理層設備(PHY)接口

- 支持AXI-Stream接口

- 支持10/100/1000Mbps速度

任意運行計時器功能

- 由用戶完全管理(時間和頻率調整)

時間同步

- 支持第2層PTP(單端口和雙端口)

- 支持第3層PTP(單端口)

- 支持的配置文件:電源配置文件,實用程序配置文件,IEC61850配置文件和默認配置文件

- 可用的輸出計時器:“ 64位納秒”或“ 48位秒 + 32位納秒”

- 提供PPS輸出

- 可選的IRIG-B主站輸出與PTP內部定時器同步(DCLS和AM調制)

- 支持事件時間戳

- 支持警報檢測

參考設計支持的板

- SoC-e SMARTzynq brick(推薦)

欲了解更多信息,請聯系我們:info@aiportek.com

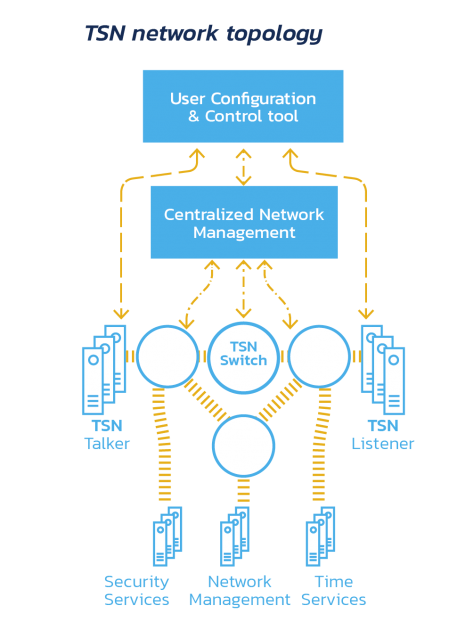

與時俱進 銳意創新——與虹科一起探索TSN的更多潛力

時間敏感網絡(Time Sensitive Networking,TSN) ,是基於標準以太網架構演進的新一代網絡技術,它以傳統以太網為網絡基礎,通過時鐘同步、數據調度、 網絡配置等機制,提供確定性數據傳輸能力的數據鏈路層協議規範。與傳統以太網相比,TSN能夠提供微秒級確定性服務,降低整個通信網絡覆雜度,實現信息技術 (IT)與運營技術(OT)融合,其具有精準的時鐘同步能力、確定性流量調度能力,以及智能開放的運維管理架構,可以保證多種業務流量的共網高質量傳輸, 兼具性能及成本優勢,是未來網絡的發展趨勢。

目前,TSN技術在汽車、工業、軌道交通、航空航天領域有著較高的討論熱度,它作為一項非供應商綁定的實時通訊協議,我們認為TSN技術有著不錯的應用前景。

歡迎聯系我們與您一起探討學習TSN技術與各行各業的結合,並積極推動更多落地應用,共同構建智能互聯的新世界。