- Home

- Technical Products

Enterprise Cloud IT Solutions

Industrial Measurement

- Solutions

Enterprise Cloud IT Solutions

Test Measurement

- Latest Articles

- About Us

EN

EN

10G Managed Ethernet Switch IP Cores

Product Overview

The Unmanaged Ethernet Switch IP core (UES) enables plug-and-play Ethernet switching on configurable devices. It requires no external configuration and is designed to maximize throughput using minimal resources.

The switch implements a non-blocking cross-switching matrix that allows wire-speed communication between all ports. The switch caches and verifies each frame before forwarding it. However, wait times are minimized to the nanosecond level. In addition, the UES supports the IEEE 1588 V2 transparent clock feature. This feature corrects erroneous PTP frames introduced into the switch, thus maintaining the highest level of accuracy in the interconnection between IEEE 1588 synchronous devices.

UES is the ideal Ethernet switch IP for implementing Ethernet-based industrial networks. it provides MII/GMII/RGMII native interfaces for Ethernet PHY devices and can be used in conjunction with Xilinx IP to support RMII or SGMII in other interfaces. it also supports connecting AXI4-Stream interfaces to other IP kernels that do not have a MAC-based interface. It also supports connecting the AXI4-Stream interface to other cores that do not have a MAC-based interface.

Key Features of Unmanaged Ethernet Switch IP Cores

- Plug and play: no configuration required

- High performance: full cross-matrix between ports for maximum throughput

- Fast: Significantly reduced latency due to SoC-e's proprietary MAC address matching mechanism

- Efficient: optimized for implementation on low-cost FPGA devices with minimal logic resources

- Flexible: Fully scalable and configurable for optimal function-size balance. The following parameters are available to designers:

○Number of ports: 3 to 16 configurable Ethernet ports

○Muffler queue length

○IEEE Transparent Clock Function

- Automatic: MAC address learning and aging (by default, the storage capacity is 2048 MAC addresses).

The following Xilinx FPGA families can support UES

Easily integrate UES into your FPGA designs by utilizing the new Xilinx Vivado tool, which allows IP parameters to be configured in a simple manner using the IP core in a graphical user interface.

Reference Design Supported Boards

- SoC-e SMARTzynq brick(Recommended)

Keeping up with the times and innovating - Explore more potentials of TSN with Hongke

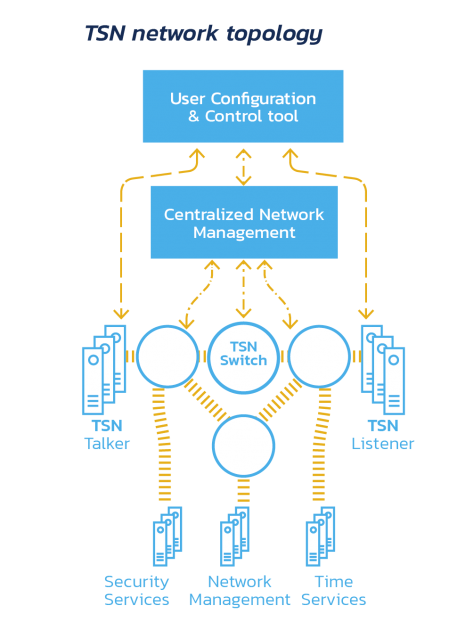

Time Sensitive Networking (TSN) is a new generation of network technology based on the evolution of the standard Ethernet architecture. It takes traditional Ethernet as the network foundation and provides a data link layer protocol specification for deterministic data transmission capability through mechanisms such as clock synchronization, data scheduling, and network configuration. Compared with traditional Ethernet, TSN can provide microsecond-level deterministic services, reduce the complexity of the entire communication network, and realize the convergence of information technology (IT) and operation technology (OT). With its precise clock synchronization, deterministic traffic scheduling, and intelligent and open operation and maintenance management framework, TSN can ensure the high-quality transmission of multiple business traffic in a common network, and it has both performance and cost advantages, and it is the development trend of the future network. This is the future trend of network development.

Currently, TSN technology has a high level of discussion in the automotive, industrial, rail transportation, and aerospace fields. As a non-vendor-bound real-time communication protocol, we believe that TSN technology has a good application prospect.

Welcome to contact us to explore and learn the integration of TSN technology with various industries, and actively promote more applications on the ground to jointly build a new world of intelligent interconnection.