精確時間基礎IP核

IEEE1588v2普通和邊界時鐘

精確時間基礎是Xilinx FPGA的IEEE1588-2008 v2兼容時鐘同步IP內核。它能夠準確地為IEEE 1588報文打上時間戳,並提供兼容的計時器。所有這些過程均由硬件模塊執行。

精確時間基礎IP包含不同的硬件和軟件元素:

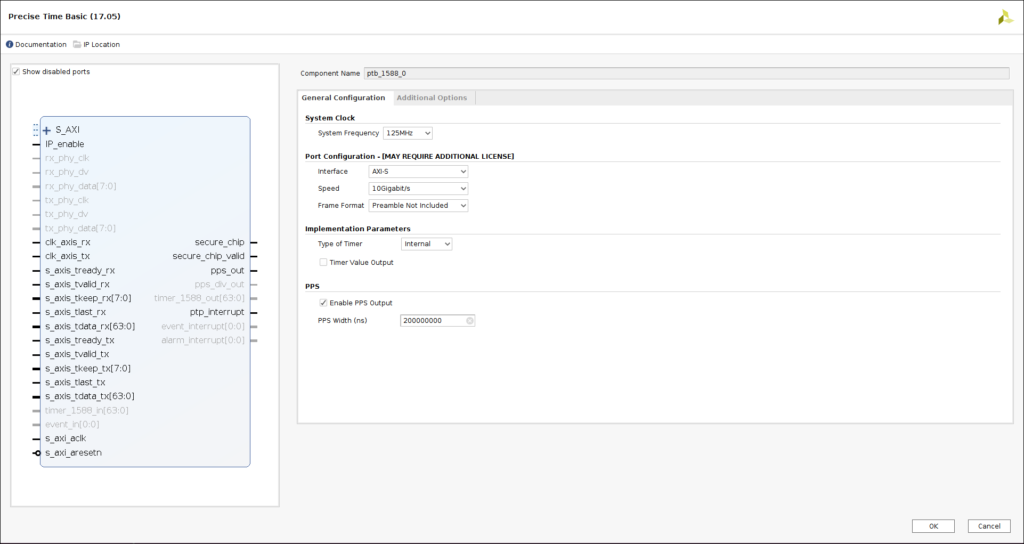

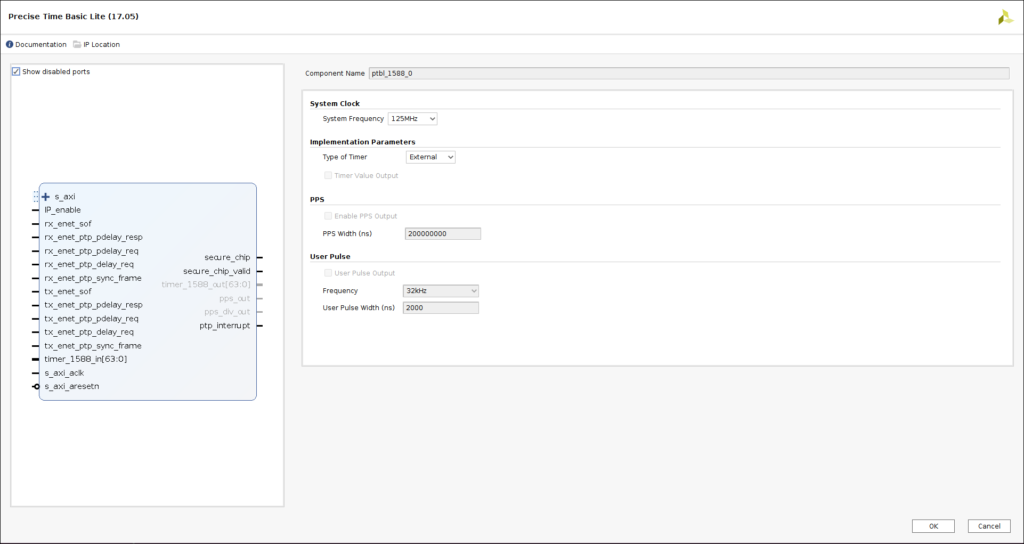

- 硬件時間戳單元(TSU)能夠準確地為IEEE 1588事件消息加時間戳,並提供具有亞微秒精度的可調計時器。實際上,精確時間基礎提供了兩種版本的TSU:PTB TSU和PTBLite TSU。

- PTB TSU被設計為連接到MAC和PHY之間的介質獨立接口([G] MII),解析所有以太網幀並檢查哪些是IEEE 1588。

- PTBLite TSU利用Zynq GMAC中包含的PTP解析器,以使用較少的FPGA資源來提供TSU,但PS GMAC上的IEEE 1588硬連線邏輯施加了一些限制。

兩種版本的TSU都可以使用內部可調定時器或從另一個TSU獲取其定時器值。因此,多個以太網連接可以共享同一計時器,或者不同的以太網連接可以具有各自的計時器。

- PTB TSU被設計為連接到MAC和PHY之間的介質獨立接口([G] MII),解析所有以太網幀並檢查哪些是IEEE 1588。

- PTBLite TSU利用Zynq GMAC中包含的PTP解析器,以使用較少的FPGA資源來提供TSU,但PS GMAC上的IEEE 1588硬連線邏輯施加了一些限制。

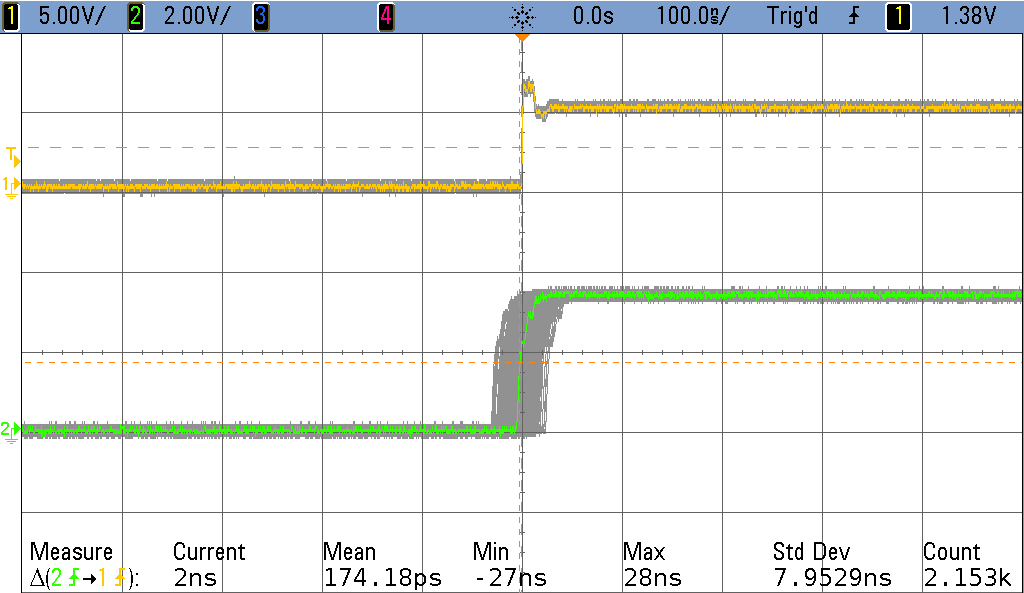

在IEEE 1588系統中獲得的最終精度取決於許多因素(本地時鐘的頻率和質量,數據鏈中時間戳的位置等)。作為參考,上圖顯示了商業Grandmaster設備生成的PPS與Zedboard Avnet Devopment Platfrom生成的PPS之間的測量誤差,Zedboard Avnet Devopment Platfrom在ARM處理器中運行LinuxPTP軟件堆棧,並使用精確時間基礎進行硬件輔助時間戳(+/-50 ns)。

硬件功能

- 支持10/100/1000Mbps/AXI-Stream(用於10Gbps/25Gbps)接口

- 32位秒/32位納秒計數器

- 32位亞納秒頻率調整

- 每秒一脈沖輸出

- 可選頻率輸出(1 KHz/2 KHz/4 KHz/8 KHz/16 KHz/32 KHz)

- 最低的FPGA資源利用率

- 警報生成

- 事件時間戳記

軟件功能

- 普通時鐘(主站和從站)操作

- 端到端和點對點延遲機制支持

- 在第2層(以太網)和第3層(IPv4)接口上均支持PTP

- 它可以與HSR-PRP和網管以太網IP內核結合使用

- VLAN支持

- 工業配置文件:默認、電源、電源實用程序IEC 61850-9-3、IEEE 802.1AS

- 汽車配置文件:IEEE 802.1AS通用PTP(gPTP)配置文件

- 企業配置文件/5G/電信配置文件:G.8265.1,G.8275.1和G.8275.2

Xilinx FPGA系列支持

以下Xilinx FPGA系列可以支持精確時間基礎:

- 7-Series (Zynq SoC, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

通過利用新的Xilinx Vivado工具,可以輕松地將其集成到你的FPGA設計中,該工具允許在圖形用戶界面中使用IP內核,並以簡便的方式配置IP參數。

參考設計支持的板

SoC-e SMARTzynq brick(推薦)

與時俱進 銳意創新——與虹科一起探索TSN的更多潛力

時間敏感網絡(Time Sensitive Networking,TSN) ,是基於標準以太網架構演進的新一代網絡技術,它以傳統以太網為網絡基礎,通過時鐘同步、數據調度、 網絡配置等機制,提供確定性數據傳輸能力的數據鏈路層協議規範。與傳統以太網相比,TSN能夠提供微秒級確定性服務,降低整個通信網絡覆雜度,實現信息技術 (IT)與運營技術(OT)融合,其具有精準的時鐘同步能力、確定性流量調度能力,以及智能開放的運維管理架構,可以保證多種業務流量的共網高質量傳輸, 兼具性能及成本優勢,是未來網絡的發展趨勢。

目前,TSN技術在汽車、工業、軌道交通、航空航天領域有著較高的討論熱度,它作為一項非供應商綁定的實時通訊協議,我們認為TSN技術有著不錯的應用前景。

歡迎聯系我們與您一起探討學習TSN技術與各行各業的結合,並積極推動更多落地應用,共同構建智能互聯的新世界。