- Home

- Technical Products

Enterprise Cloud IT Solutions

Industrial Measurement

- Solutions

- Latest Articles

- About Us

EN

EN

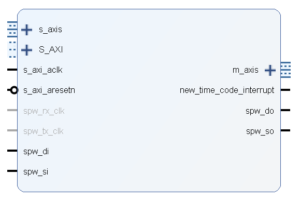

SpaceWire IP core

The SpaceWire protocol is a standard for high-speed links and networks on airborne spacecraft that simplifies the interconnection between sensors, mass storage, processing units and downlink telemetry subsystems. It is a full-duplex, bidirectional, serial, point-to-point data link. It uses two differential pairs in each direction to encode the data. There are a total of eight signal lines, four in each direction.SpaceWireRDDP may be suitable for many aerospace microelectronic devices, such as spacecraft systems, bus systems, and embedded microcontrollers. The European Space Agency (ESA) has coordinated the evolution of this spacecraft communications network standard in cooperation with international space agencies including NASA, JAXA and RKA.

Product Overview

The SpaceWire IP core is a VHDL kernel that implements a complete, reliable and fast SpaceWire codec with an AXI management interface for synthesizing FPGAs and configurable SoC devices.

The IP core can run up to the packet level in a peer-to-peer link without a "destination address" and is designed to be ECSS-E-ST-50-12C compliant. It is designed to comply with ECSS-E-ST-50-12C. SpaceWire IP supports both general-purpose and fast implementation modes, where the transmitter is designed to support bit rates up to 5 times the system clock frequency.

The following Xilinx FPGA families support SpaceWire IP:

Series 7 (Zynq, Spartan, Artix, Kintex, Virtex)

Ultrascale (Kintex, Virtex)

Ultrascale + (Zynq MPSoC, Kintex, Virtex)

XQR Series (Space Class FPGA): Virtex-5QV

Seamlessly integrate SpaceWire IP into your FPGA designs by utilizing the new Xilinx Vivado tool, which allows IP parameters to be configured in a simple way using the IP core in a graphical user interface.

data interface

- Rx bit rate up to x4 of system clock frequency

- Tx clock frequency between 100MHz and 625MHz

- Separate Clock Fields

FIFO configuration

- Tx FIFO depth is fully configurable: from 64 bytes to 16384 bytes

- RX FIFO depth fully configurable: from 64 bytes to 16384 bytes

connector

- AXI streams (data)

- AXI-4 Lite (configuration and management)

performances

- Up to 200Mbps link speeds

SoC-e's SMARTcia board can support SpaceWire IP cores, specialized for space environments on a platform that meets current regulatory requirements.

有關此IP、許可模式和基於此標準的交鑰匙項目的更多信息,請聯系我們:info@aiportek.com

Keeping up with the times and innovating - Explore more potentials of TSN with Hongke

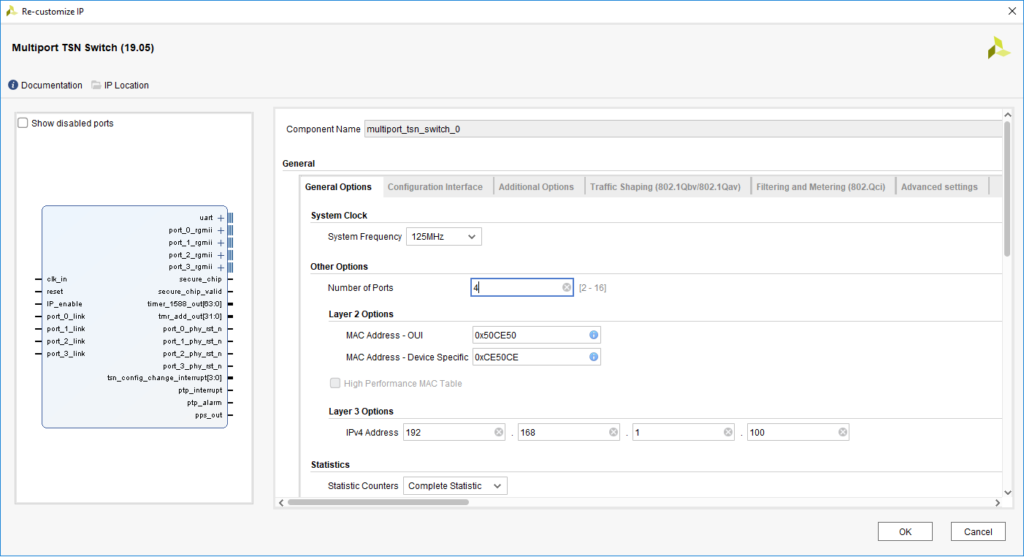

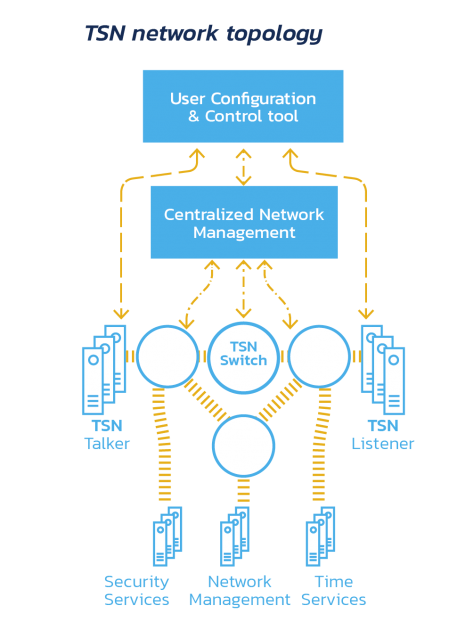

Time Sensitive Networking (TSN) is a new generation of network technology based on the evolution of the standard Ethernet architecture. It takes traditional Ethernet as the network foundation and provides a data link layer protocol specification for deterministic data transmission capability through mechanisms such as clock synchronization, data scheduling, and network configuration. Compared with traditional Ethernet, TSN can provide microsecond-level deterministic services, reduce the complexity of the entire communication network, and realize the convergence of information technology (IT) and operation technology (OT). With its precise clock synchronization, deterministic traffic scheduling, and intelligent and open operation and maintenance management framework, TSN can ensure the high-quality transmission of multiple business traffic in a common network, and it has both performance and cost advantages, and it is the development trend of the future network. This is the future trend of network development.

Currently, TSN technology has a high level of discussion in the automotive, industrial, rail transportation, and aerospace fields. As a non-vendor-bound real-time communication protocol, we believe that TSN technology has a good application prospect.

Welcome to contact us to explore and learn the integration of TSN technology with various industries, and actively promote more applications on the ground to jointly build a new world of intelligent interconnection.