- Home

- Technical Products

Enterprise Cloud IT Solutions

Test Measurement

Industrial Measurement

- Solutions

Enterprise Cloud IT Solutions

Test Measurement

- Latest Articles

- About Us

EN

EN

IRIGtimeM

IRIG-B master IP core

IRIGtimeM implements an IRIG 200-04-compatible time synchronization master on an FPGA device. This IRIG-B master IP is designed to support all IRIG-B encoded expressions as well as DCLS and AM modulation to provide maximum flexibility.

This IRIG-B master IP generates IRIG-B frames per second, including mandatory and optional time information (seconds, minutes, hours, days, years, control functions, and consecutive binary seconds), depending on the IRIG-B time code selected on the configuration. The IP is capable of supporting autonomous operation and requires excessive configuration.

The following Xilinx FPGA families support IRIG timeM:

- 7-Series (Zynq SoC, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

Managed Ethernet Switch IP Core for Xilinx Vivado Tools

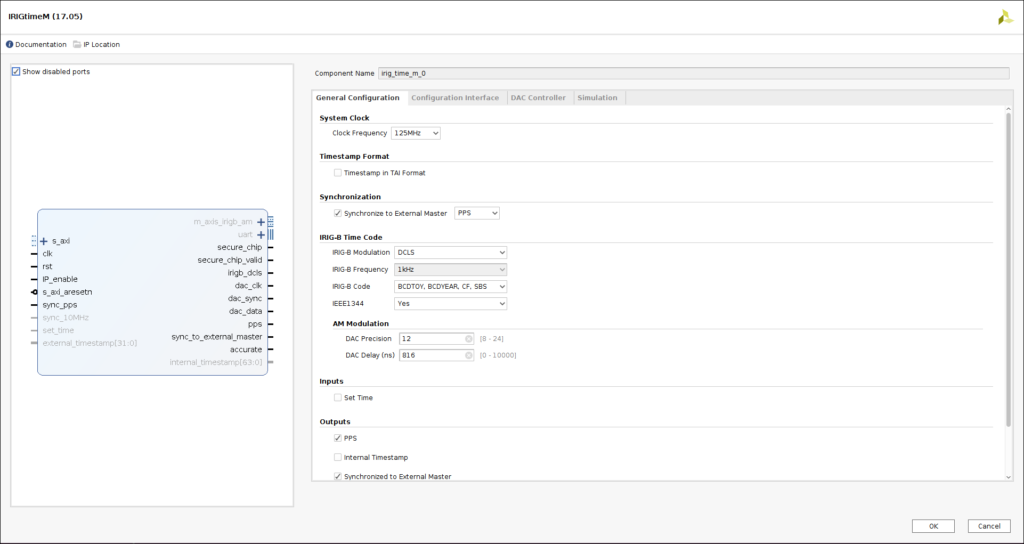

Integration into your FPGA designs is made easy by utilizing the new Xilinx Vivado tool, which allows IP cores to be used in a graphical user interface and IP parameters to be configured in an easy way.

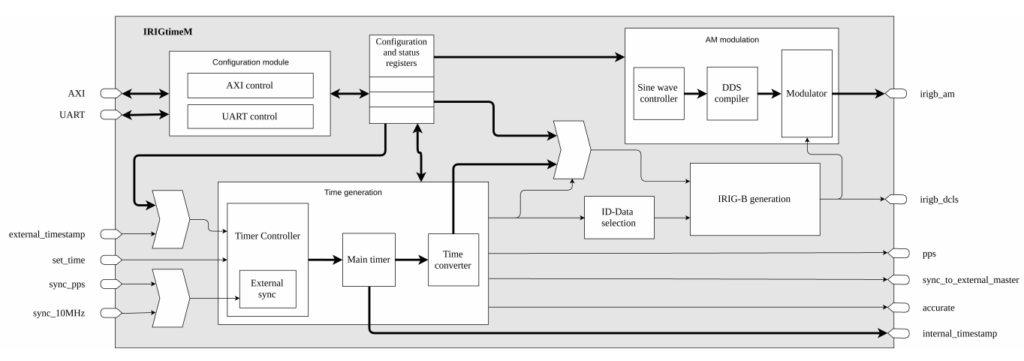

The block diagram of the IRIGtimeM IP core is shown below

IRIGtimeM Main Features

- IRIG 200-04 compliant time synchronization masters

- Supports DCLS and AM modulation

- Supports all IRIG-B encoded expressions, including year information, control functions and linear binary seconds

- Output type (IRIG-B time code) can be configured before implementation and during operation

- Precision IRIG-B output for nanosecond accuracy

- 32-bit timestamp input for initial IP settings

- Periodic pulse output for testing

Reference Design Supported Boards

- SoC-e SMARTzynq brick (recommended)

Keeping up with the times and innovating - Explore more potentials of TSN with Hongke

Time Sensitive Networking (TSN) is a new generation of network technology based on the evolution of the standard Ethernet architecture. It takes traditional Ethernet as the network foundation and provides a data link layer protocol specification for deterministic data transmission capability through mechanisms such as clock synchronization, data scheduling, and network configuration. Compared with traditional Ethernet, TSN can provide microsecond-level deterministic services, reduce the complexity of the entire communication network, and realize the convergence of information technology (IT) and operation technology (OT). With its precise clock synchronization, deterministic traffic scheduling, and intelligent and open operation and maintenance management framework, TSN can ensure the high-quality transmission of multiple business traffic in a common network, and it has both performance and cost advantages, and it is the development trend of the future network. This is the future trend of network development.

Currently, TSN technology has a high level of discussion in the automotive, industrial, rail transportation, and aerospace fields. As a non-vendor-bound real-time communication protocol, we believe that TSN technology has a good application prospect.

Welcome to contact us to explore and learn the integration of TSN technology with various industries, and actively promote more applications on the ground to jointly build a new world of intelligent interconnection.