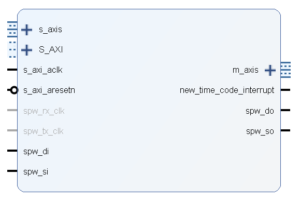

SpaceWire IP核

SpaceWire協議是機載航天器上用於高速鏈路和網絡的標準,簡化傳感器、大容量存儲器、處理單元和下行鏈路遙測子系統之間的互連。它是全雙工、雙向、串行、點對點數據鏈路。它在每個方向上使用兩個差分對對數據進行編碼。總共有八根信號線,每個方向有四根。SpaceWireRDDP可能適用於許多航空航天微電子設備,例如航天器系統、總線系統和嵌入式微控制器。歐洲航天局(ESA)與包括NASA、JAXA和RKA在內的國際航天機構合作,協調了該航天器通信網絡標準的演變。

產品概述

SpaceWire IP核是VHDL內核,它實現了具有AXI管理接口的完整、可靠和快速的SpaceWire編解碼器,為FPGA和可配置的SoC器件進行合成。

該IP核可以在沒有“目標地址”的點對點鏈接中運行到數據包級別。它的設計符合ECSS-E-ST-50-12C。SpaceWire IP支持通用和快速兩種實現模式,其中發送器被設計為支持比特率高達5倍系統時鐘頻率。

以下Xilinx FPGA系列支持SpaceWire IP:

7系列(Zynq,Spartan,Artix,Kintex,Virtex)

Ultrascale(Kintex,Virtex)

Ultrascale +(Zynq MPSoC,Kintex,Virtex)

XQR系列(太空級FPGA):Virtex-5QV

通過利用新的Xilinx Vivado工具,可以將SpaceWire IP無縫集成到您的FPGA設計中,該工具允許在圖形用戶界面中使用IP內核並以簡單的方式配置IP參數。

數據接口

- Rx比特率高達系統時鐘頻率的x4

- Tx時鐘頻率在100MHz-625MHz之間

- 單獨的時鐘域

FIFO配置

- Tx FIFO深度完全可配置:從64字節到16384字節

- RX FIFO深度完全可配置:從64字節到16384字節

接口

- AXI流(數據)

- AXI-4 Lite(配置和管理)

性能

- 高達200Mbps的鏈接速度

SoC-e的SMARTcia板可支持SpaceWire IP核,專用於空間環境的一個平台,可滿足當前法規要求。

有關此IP、許可模式和基於此標準的交鑰匙項目的更多信息,請聯系我們:info@aiportek.com

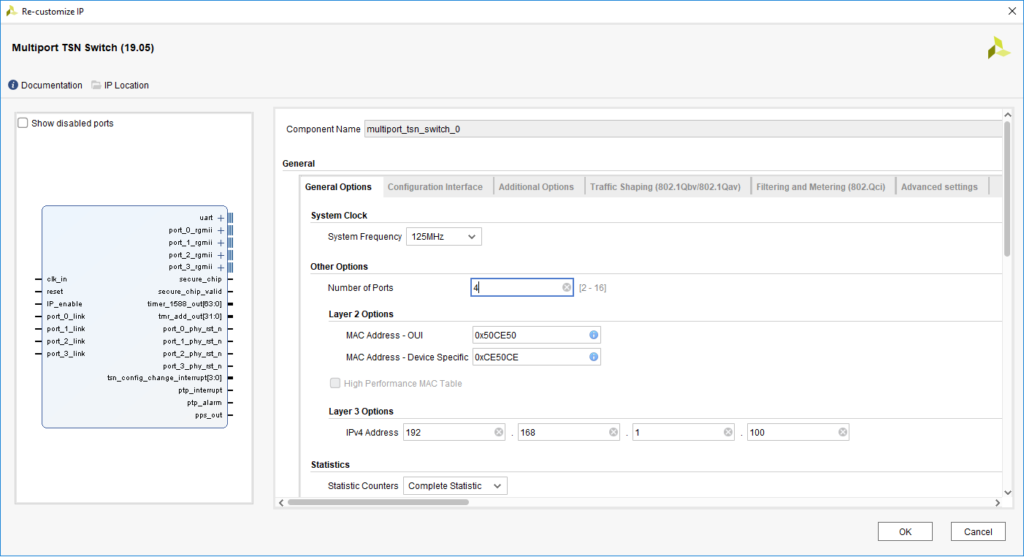

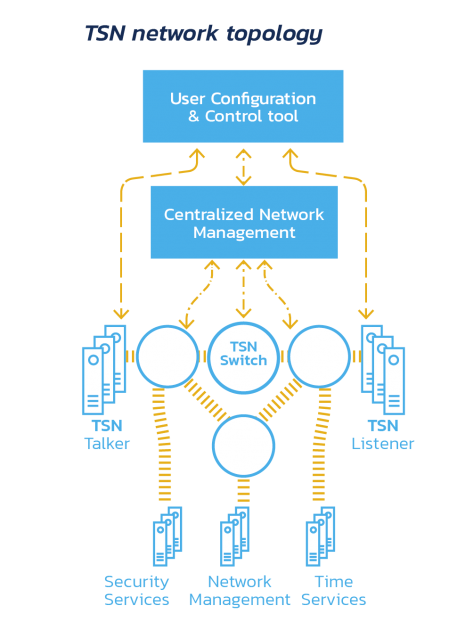

與時俱進 銳意創新——與虹科一起探索TSN的更多潛力

時間敏感網絡(Time Sensitive Networking,TSN) ,是基於標準以太網架構演進的新一代網絡技術,它以傳統以太網為網絡基礎,通過時鐘同步、數據調度、 網絡配置等機制,提供確定性數據傳輸能力的數據鏈路層協議規範。與傳統以太網相比,TSN能夠提供微秒級確定性服務,降低整個通信網絡覆雜度,實現信息技術 (IT)與運營技術(OT)融合,其具有精準的時鐘同步能力、確定性流量調度能力,以及智能開放的運維管理架構,可以保證多種業務流量的共網高質量傳輸, 兼具性能及成本優勢,是未來網絡的發展趨勢。

目前,TSN技術在汽車、工業、軌道交通、航空航天領域有著較高的討論熱度,它作為一項非供應商綁定的實時通訊協議,我們認為TSN技術有著不錯的應用前景。

歡迎聯系我們與您一起探討學習TSN技術與各行各業的結合,並積極推動更多落地應用,共同構建智能互聯的新世界。